行业资讯

NAND Flash 芯片测试讲解【干货】

22-03-31 09:32:09 来源:存储器

DFT : Design For TestabilityNAND Flash 芯片测试主要是为了筛选(Screen Out)出Flash阵列、译码器、寄存器的失效。从wafer level,到single component level、module level,定义各项测试的次序,筛选出性能较差和失效的device,需要尽可能达到最好的测试覆盖率,避免最后出货的产品中有失效的产品,同时需要减少测试的时间与成本。普遍来说,是为了了解产品的潜在失效分析而在一定条件下(高温/高电压/一定湿度)下加速芯片老化,以至于故障提前出现。这种测试侧重在封装相关层面,包括化学和机械等因素。这个时候测试设备就显得尤为重要了。因为在日常生活中,这样的高压环境是几乎不会出现的,测试者只能借助设备来达到测试的条件。例如,使用SSD可程式高低温老化试验箱。【点击蓝色字体查看详情】

这种试验箱在老化测试过程中可提供可以-60到150℃、温度精度达到±0.1℃的恶劣环境,并且在测试过程中,SSD还可以在温度呈现变化、一定湿度的环境下进行测试。

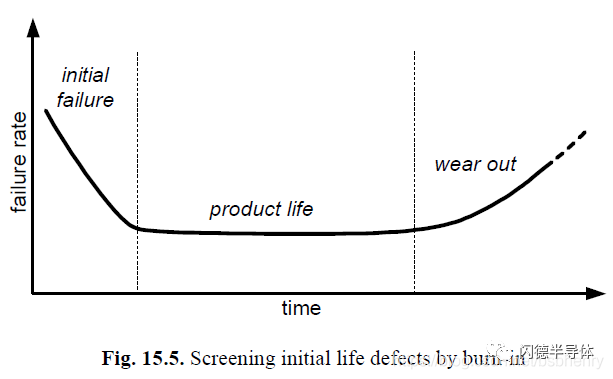

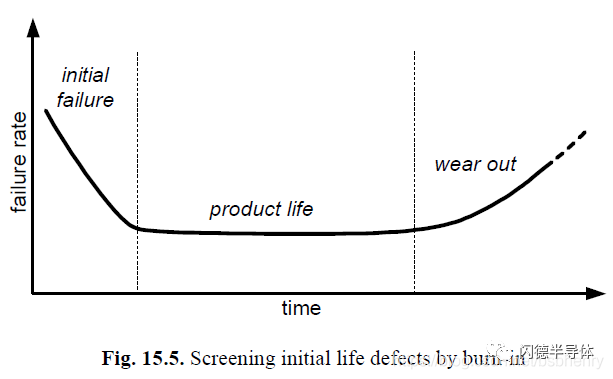

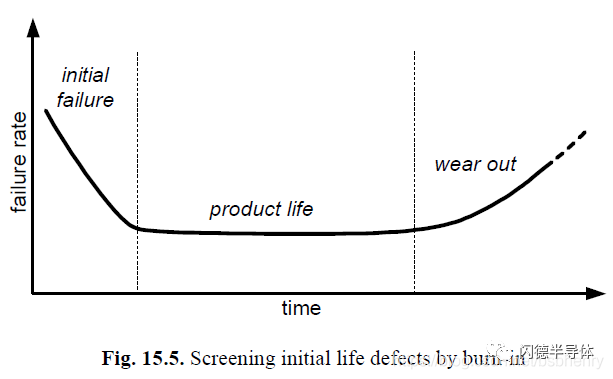

根据浴盆曲线,产品的早期失效率较高,中间阶段比较稳定。为了让用户拿到的产品失效率较低,就要通过burn-in测试,剔除有缺陷的产品,让出货的产品在出厂前就度过早夭期。为了减少时间,需要进行加速,即在更恶劣的条件下试验(高温/高电压/一定湿度),而且根据理论可以计算出不同条件下的加速因子,根据实际时间计算出等效的时间。 测试机台在测试一批产品时,必须等待所有产品都完成后,才能开始下一阶段的测试。写读擦的时间由芯片特性决定,可以努力的方向在于如何同时对多个chip或block进行操作。如果芯片可以自己生成测试数据,就可以节约数据输入的时间,这点可以通过DFT实现。如果可以直接得到测试成功失败的信息,不需要将原始的数据传输到测试机上,也可以节约大量时间。

测试机台在测试一批产品时,必须等待所有产品都完成后,才能开始下一阶段的测试。写读擦的时间由芯片特性决定,可以努力的方向在于如何同时对多个chip或block进行操作。如果芯片可以自己生成测试数据,就可以节约数据输入的时间,这点可以通过DFT实现。如果可以直接得到测试成功失败的信息,不需要将原始的数据传输到测试机上,也可以节约大量时间。

![]()

![]()